Ongoing Research

Modular and Multilevel Converters

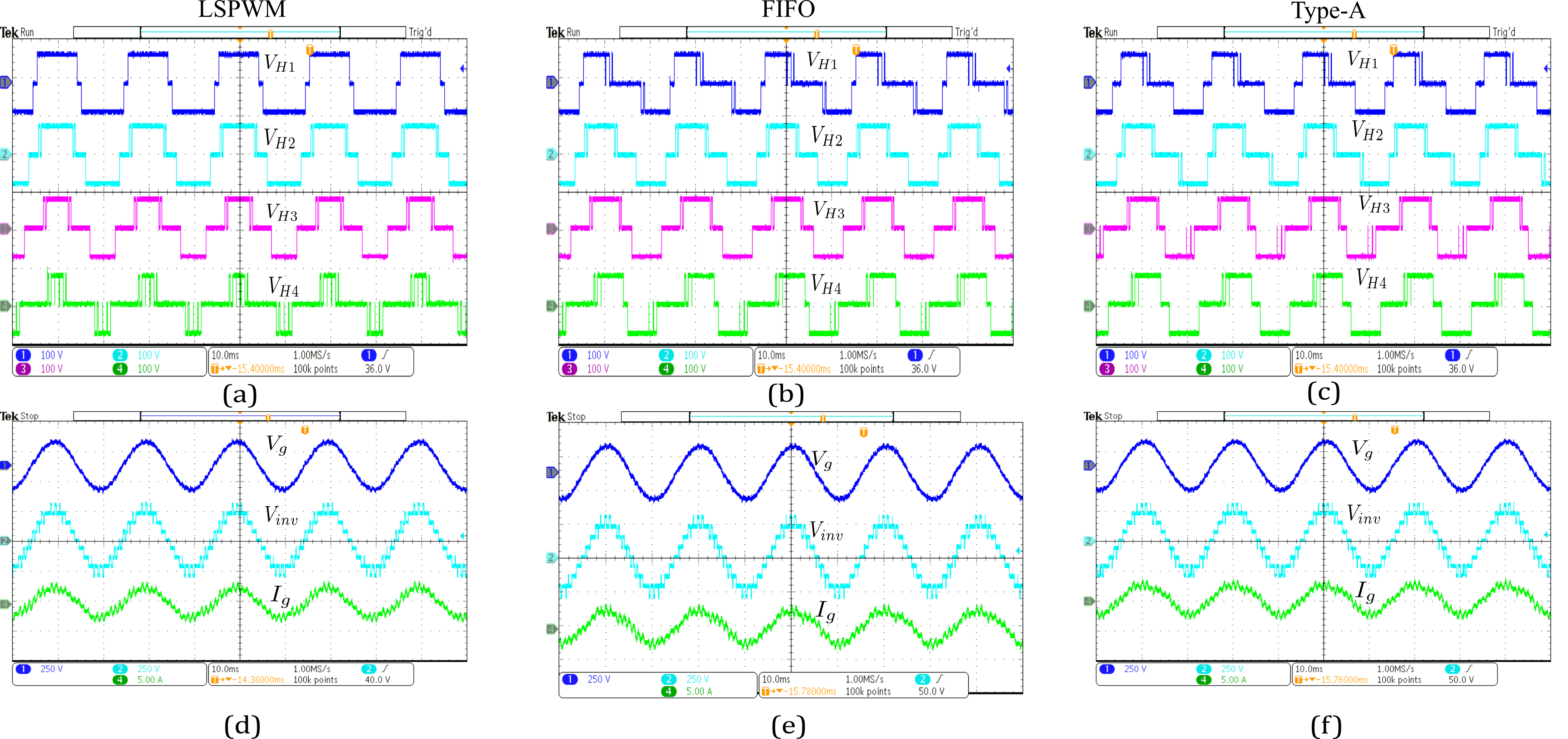

Cascaded H-Bridge (CHB) multilevel inverters are popular because of their inherent modularity, scalability, and efficient voltage translation capability. Carrier-based modulation schemes such as Level-Shifted PWM (LSPWM) are simple and easy to implement but result in extreme disparity in processed power among the modules. This unequal loading and non-uniform semiconductor loss results in unequal thermal stress, accelerating premature failures in over-stressed modules. Space-vector and switching angle adjustment schemes can remedy this but can be computationally impractical for higher-order CHBs.

Our work has led to the development of new, computationally efficient carrier-reassignment schemes for 9-level and 17-level CHB inverters to achieve near-perfect real and reactive power balance across modules over the entire power factor range. Further, semiconductor loss analysis shows that conduction and switching losses are also equalized across the topology. A simple combinational circuit is also developed to balance the zero-state conduction losses without introducing additional switching.

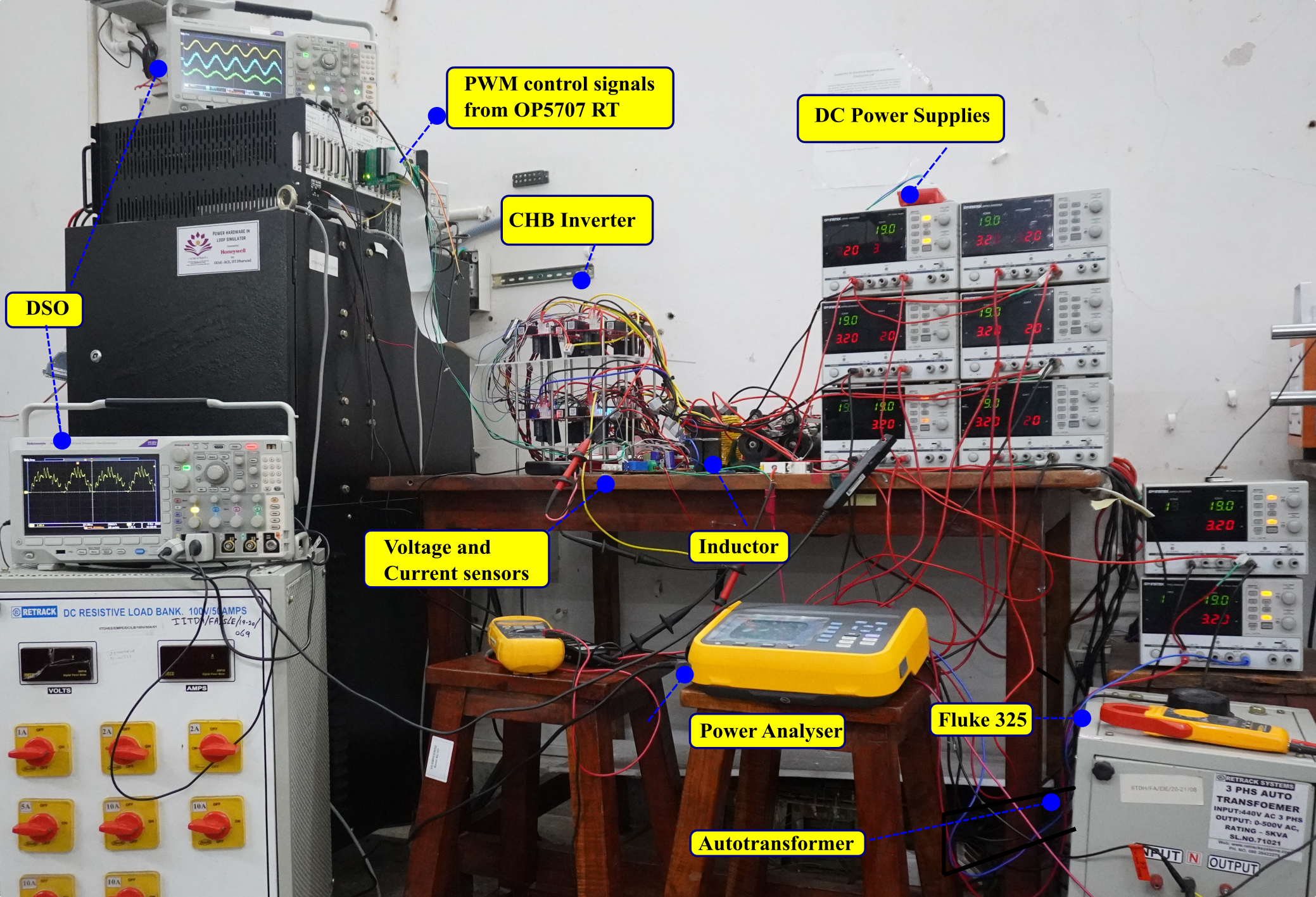

A 9-level CHB Power stage is developed for hardware testing and detailed loss models are made in Real-time simulation using the state-of-the-art OpalRT HIL Platform.

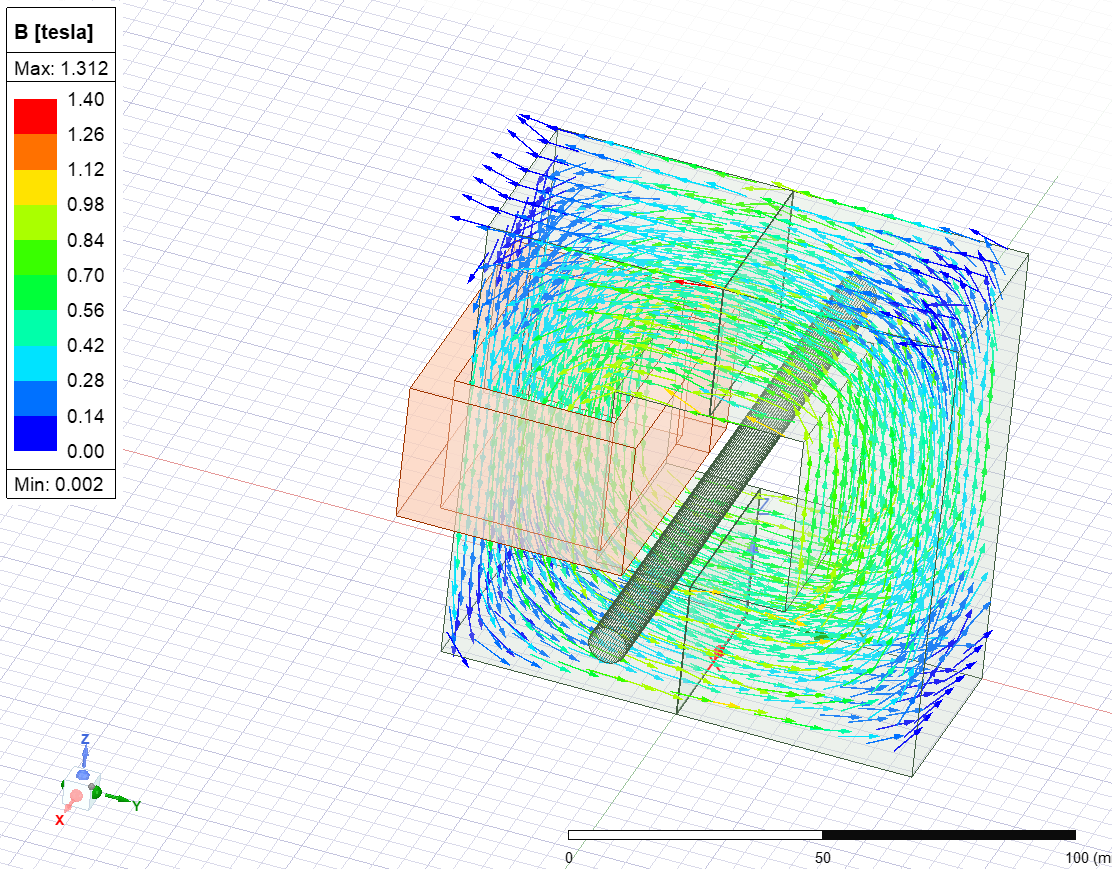

Magnetics Design for Power Harvesting

Patent Pending:

A power harvester for line-crawling robots for Live Powerline inspection